# 2D Steep-Slope Tunnel Field-Effect Transistors Tuned by van der Waals Ferroelectrics

Xinrui Chen, Tiantian Jiang, Hanbin Wang, Yang Wang,\* Miao Zhang, Yi Cui, Yong Wang, Nannan Li, Xinchuan Du, Chaoyi Yan, Yuqing Liu,\* and Xianfu Wang\*

sPower consumption has emerged as a central concern in the realm of complementary metal-oxide-semiconductor (CMOS) technology. Silicon-based semiconductor devices have now approached the fundamental thermionic limit of the subthreshold swing (SS), which is 60 mV dec $^{-1}$ , as defined by the Boltzmann tyranny. Tunnel field-effect transistors (TFETs) are considered promising low-power devices due to the band-to-band tunneling mechanism, which effectively avoids the thermionic limit. However, TFETs require the establishment of a staggered band alignment and currently lack effective techniques for adjusting the band offset. Here, by harnessing the robust ferroelectric field inherent to 2D CuInP<sub>2</sub>S<sub>6</sub> (CIPS), a 2D WSe<sub>2</sub>/MoS<sub>2</sub> heterojunction as well as a WSe<sub>2</sub> homojunction TFET controlled by ferroelectric gate are presented. The newly developed TFET achieves an ultra-low SS of 14.2 mV dec<sup>-1</sup> at room temperature, an on/off current ratio exceeding 10<sup>8</sup>, and a minimal hysteresis window below 10 mV. Additionally, the device demonstrates gate tunable negative differential resistance (NDR) characteristics with a very large peak-to-valley current ratio (PVCR) of 10.56 at room temperature. These findings underscore the significant promise of 2D ferroelectric tuning heterojunction and homojunction for future low-power electronic applications.

X. Chen, T. Jiang, Y. Wang, M. Zhang, Y. Cui, Y. Wang, X. Du, C. Yan, Y. Liu, X. Wang

State Key Laboratory of Electronic Thin Film and Integrated Devices University of Electronic Science and Technology of China Chengdu 610054, P. R. China

E-mail: yangwang@uestc.edu.cn; yuqing\_liu@uestc.edu.cn; xfwang87@uestc.edu.cn

H. Wang, N. Li Microsystem & Terahertz Research Center China Academy of Engineering Physics (CAEP) Chengdu 610200, P. R. China H. Wang, N. Li Institute of Electronic Engineering China Academy of Engineering Physics (CAEP) Mianyang 621900, P. R. China

The ORCID identification number(s) for the author(s) of this article can be found under https://doi.org/10.1002/aelm.202400463

© 2024 The Author(s). Advanced Electronic Materials published by Wiley-VCH GmbH. This is an open access article under the terms of the Creative Commons Attribution License, which permits use, distribution and reproduction in any medium, provided the original work is properly cited.

#### DOI: 10.1002/aelm.202400463

1. Introduction

Power consumption poses a significant barrier to the advancement of future CMOS chips, as it directly impacts processing speed and heat dissipation efficiency.<sup>[1–7]</sup> However, the subthreshold swing (SS), a critical indicator of power consumption in conventional MOSFETs, is limited to a value of 60 mV dec<sup>-1</sup> at room temperature due to the inherent thermal characteristics associated with carrier injection.<sup>[8,9]</sup> Presently, there are various types of devices, such as tunnel fieldeffect transistors (TFETs), negative capacitance field-effect transistors (NCFETs), cold source field-effect transistors (CS-FET), and impact ionization field-effect transistors (IFET), which have demonstrated the ability to overcome the restriction imposed by thermal emission.<sup>[10-13]</sup> From the perspective of advancing carrier transport strategies, TFETs, featuring staggered band alignment between the source and channel to promote carrier mobility through the tunneling

effect, demonstrate potential in overcoming this limitation.<sup>[14,15]</sup> However, prior to its feasible integration into practical applications, several hurdles should be navigated.<sup>[10]</sup> First, the inadequate modulation of the electrostatic gate impedes the formation of favorable band alignment conducive to tunneling. Furthermore, dangling bonds in bulk materials frequently result in interfacial defects and lattice mismatches, which also detrimentally impact the SS. Therefore, the selection of appropriate materials for TFET construction that can achieve a staggered bandgap alignment and simultaneously enable optimal device performance free from interface issues has indeed become a critical concern.

The advancement of 2D materials presents significant opportunities for TFETs due to their atomic-thin characteristic, allowing for a potent electrostatic control.<sup>[16–22]</sup> Additionally, 2D materials exhibit unique ability to facilitate the arbitrary stacking of various functional materials without requiring lattice matching, attributable to the weak interactions known as van der Waals forces.<sup>[23–28]</sup> Coupled with an appreciably larger surfaceto-volume ratio, these TFETs incorporating 2D materials offer the advantage of enhanced electrostatic control from the gate,

**1DVANCED** CIENCE NEWS www.advancedsciencenews.com

increased conductivity, and excellent interface contact with the gate insulator.<sup>[29]</sup> For example, previous researches have elucidated that the substitution of traditional silicon with atomic-thin MoS<sub>2</sub> in the channel presents the potential to fabricate vertical heterostructure MoS<sub>2</sub>/Ge TFET with exceptional electrostatics and strain-free heterointerfaces, achieving an average SS of 31.1 mV dec<sup>-1</sup>.<sup>[30]</sup> Subsequently, in an endeavor to ameliorate the issue of lower conduction current levels, researchers have developed TFETs based on black phosphorus (BP).<sup>[31]</sup> Due to the advantageous property of BP, where its thickness can spatially vary without yielding interface-related issues, this bulk BP/monolayer BP device exhibits a higher on-current with an average SS of 26 mV dec<sup>-1</sup>. Despite some progress, the integration of few-layer 2D materials with bulk or 3D materials is inevitably affected by irregularities in the thickness and doping level of the semiconductor channel, significantly increasing the process complexity and hindering the full exploitation of the advantages of 2D materials. While in the case of 2D TFETs, it is essential to design the gate to achieve control over the band alignment. Firstly, conventional control gates are excluded from our consideration due to their reliance on deposition techniques, such as atomic layer deposition (ALD) which often unavoidably introduce interface defects.<sup>[32]</sup> In regard to 2D dielectric materials, represented by hexagonal boron nitride (h-BN), it has been demonstrated that they are capable of coupling with 2D channel materials, thereby providing a potential approach for the design of 2D TFETs.<sup>[33]</sup> Despite successfully addressing interface issues inherent in the manufacturing process, their modulation capacity falls short of realizing highquality TFETs. In contrast, the novel van der Waals ferroelectric materials exhibit stable and strong polarization characteristics, suggesting the potential to construct control gates with robust modulation abilities while maintaining a clean interface.<sup>[34–37]</sup>

Our device design strategy incorporates CuInP<sub>2</sub>S<sub>6</sub> (CIPS) as the controlling gate, with WSe<sub>2</sub> and MoS<sub>2</sub> serving as channel materials. The objective is to enhance gate control over the electrostatics of the tunnel junction while ensuring the clean interface. As one of the rare room-temperature 2D ferroelectric materials, CIPS exhibits switchable polarization at a thickness of approximately 4 nm and low leakage current. Its out-of-plane polarization has been extensively exploited in diverse nanoelectronic applications, effectively combining the robustness of ferroelectricity with the flexibility of van der Waals integration.[38,39] While for the channel materials, WSe<sub>2</sub> and MoS<sub>2</sub> were selected due to their well-established processing techniques. Furthermore, experiment evidence from both homojunction and heterojunction studies confirms their ability to manifest tunneling phenomena under gate modulation.<sup>[22,40-42]</sup> Consequently, they are considered suitable candidates for TFETs. Expanding on this groundwork, there is still a lack of compelling evidence and exploration concerning the integration of 2D ferroelectric gate with 2D semiconductor channels to create robust TFETs. This is precisely the focal point of our work that we endeavor to elucidate.

This article presents the successful fabrication of 2D van der Waals TFETs based on WSe<sub>2</sub>/MoS<sub>2</sub> heterojunction as well as WSe<sub>2</sub> homojunction, utilizing CIPS as the ferroelectric control gate. These devices address the thermionic limitation encountered in conventional MOSFETs, achieving a minimum SS of 28 mV dec<sup>-1</sup> for heterojunction TFETs and an impressive SS of 14.2 mV dec<sup>-1</sup> for homojunction TFETs. Attributable to the high-

www.advelectronicmat.de quality and direct interaction between the ferroelectric control

ANCED

gate and the channel material, our homojunction device demonstrates even more exceptional capabilities. It not only manifests superior attributes in terms of basic metrics of low-power devices, such as a high switch ratio  $(>10^8)$  and a minute hysteresis window (<10 mV), but also exhibits substantial promise for diverse applications related to negative differential resistance (NDR). The demonstrated NDR phenomenon validates the underlying mechanism and features a gate-adjustable peak-to-valley current ratio (PVCR) with a remarkable value of 10.56 at room temperature  $(V_{\text{CIPS}} = 1.5 \text{ V})$ , showing the prospective employment of our device within the realm of logic circuits. Additionally, the superiority of our designed concept is further confirmed through comparative experiments that make use of conventional h-BN as the dielectric gate. Our research serves as a significant demonstration of low-power devices based on ferroelectric CIPS in a fully 2D configuration.

#### 2. Results and Discussion

By employing the novel van der Waals ferroelectric material, CIPS, as a control gate, high-quality homojunction, and heterojunction TFETs were constructed on the hafnium oxide (HfO<sub>2</sub>) substrate. The process commenced with the mechanical exfoliation of pristine bulk crystals including WSe<sub>2</sub>, MoS<sub>2</sub>, and CIPS to obtain atomically thin 2D flakes. Subsequently, these materials were vertically stacked layer-by-layer utilizing the dry transfer method to create a bottom-up heterostructure.

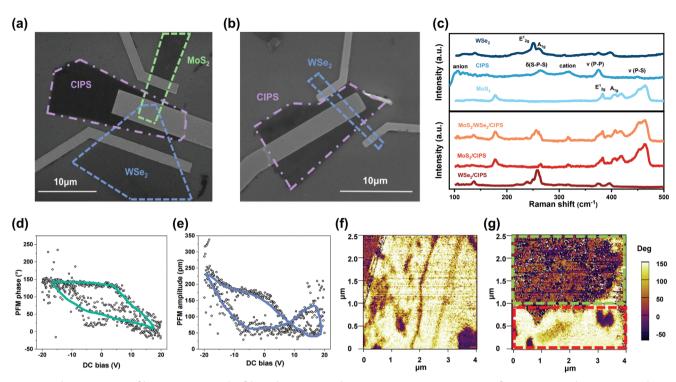

The scanning electron microscope (SEM) images of WSe<sub>2</sub>/MoS<sub>2</sub> heterojunction device and WSe<sub>2</sub> homojunction device are presented in Figure 1a,b, with CIPS stacked above a portion of the channel region to enable localized band modulation. The crystal structure of CIPS is classified under the monoclinic space group, and the vertical displacement of Cu atoms to the plane results in the generation of two different polarization states, which plays a crucial role in our devices. The vertical stacking structure and material thickness are defined using high-resolution transmission electron microscopy (TEM) in Figure S1 (Supporting Information). The thicknesses of MoS<sub>2</sub>, WSe<sub>2</sub>, and CIPS are measured to be 4.7, 3.6, and 64.3 nm, respectively. Figure 1c shows the Raman spectra of the mechanically exfoliated CIPS, MoS<sub>2</sub>, and WSe<sub>2</sub> flakes on the SiO<sub>2</sub>/Si substrate at room temperature. The Raman peaks of CIPS flake can be attributed to various vibration modes, including those at 106 cm<sup>-1</sup> corresponding to the displacement of P-P dimers, 317 cm<sup>-1</sup> due to the presence of cations. Additionally, the peaks at 264 cm<sup>-1</sup> correspond to the  $\delta$ (S–P–P) mode, 375 cm<sup>-1</sup> to the v(p-p) mode, and 450 cm<sup>-1</sup> to the v(P-S) mode. In the case of WSe<sub>2</sub> nanoflake, the Raman spectrum exhibits two typical peaks at 250 cm<sup>-1</sup> corresponding to the  $E_{2g}^1$  mode and 261 cm<sup>-1</sup> for the A1g mode. The characteristic peaks for MoS2 are observed at 383  $\text{cm}^{-1}$  for the  $\text{E}_{2g}^1$  peak and at 405  $\text{cm}^{-1}$  for the  $A_{1g}$  peak. We have also provided the Raman spectra for different areas of the heterojunction. The overlapping regions exhibit peaks corresponding to those of the individual materials, depending on their composition, thus confirming the effectiveness of the heterojunction. In the characterization of ferroelectric properties, the phase signal observed in the piezoresponse force microscopy (PFM) test of CIPS, as shown in Figure 1d, displays

www.advancedsciencenews.com

CIENCE NEWS

www.advelectronicmat.de

**Figure 1.** Characterization of heterostructures. The false-color scanning electron microscope (SEM) image of a)  $WSe_2/MOS_2$  heterojunction device and b)  $WSe_2$  homojunction device, each distinct color represents a specific type of material to differentiate the various components within the device. c) Raman spectroscopy (using a 633 nm laser) of the mechanically exfoliated CIPS,  $MOS_2$  and  $WSe_2$  flakes as well as heterojunction area on the  $SiO_2/Si$  substrate at room temperature. d) The PFM phase and e) amplitude hysteresis loops during the switching process. f) The primary PFM phase image of CIPS. g) The PFM phase image after written two-box patterns with reverse DC bias.

a clear 180° switch. Furthermore, the amplitude signal depicted in Figure 1e demonstrates a distinct butterfly loop, confirming the robust ferroelectric polarization present in the CIPS flake. To further validate the stability and controllability of ferroelectricity in our CIPS flake, we performed local polarization tests by applying bias between the conductive PFM tip and the conductive gold substrate. As shown in Figure 1f,g, opposite voltages were applied in the two designated regions marked in red and green, with the evident phase reversal serving as confirmation of polarization switching in CIPS.

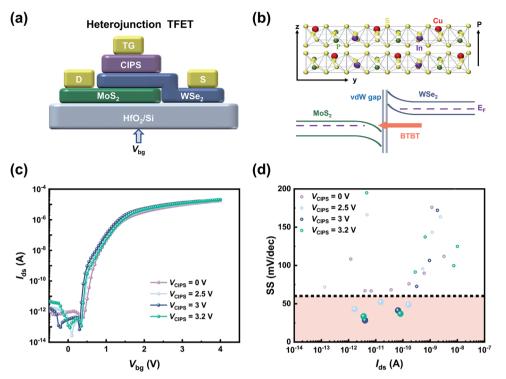

The typical structure of TFETs, while similar to traditional MOSFETs, features a channel with opposite doping types near the source and drain regions. Its operational principle resembles that of a PIN diode with a gate, which controls the band bending in the channel region via the gate, thereby regulating band-toband tunneling between the source and the channel.<sup>[30,43]</sup> Once a voltage is applied on the top control gate, the energy bands within the channel materials undergo local modulation into a staggered alignment. Figure 2a shows the TFET structure featuring a WSe<sub>2</sub>/MoS<sub>2</sub> heterojunction as the channel, with CIPS stacked in the overlap region between WSe<sub>2</sub> and MoS<sub>2</sub>. The corresponding transfer curves of the devices with the individual WSe<sub>2</sub> and MoS<sub>2</sub> as channel exhibit bipolar and n-type transfer characteristics, respectively, as shown in Figure S2 (Supporting Information). And the output characteristics of WSe<sub>2</sub>/MoS<sub>2</sub> heterojunction are depicted in Figure S3b (Supporting Information). Given that MoS<sub>2</sub> is an n-type material, it is imperative to modulate the bipolar WSe<sub>2</sub> into a p-type using CIPS in order to achieve

a staggered band alignment in this heterostructure. To experimentally investigate the actual impact of CIPS on heterojunction channels, electrical testing of the heterojunction TFET was conducted.

We systematically performed a series of transfer curves ( $V_{ds}$ = -1 V) under various ferroelectric gate conditions (Figure 2c), and the corresponding extracted SS is presented in Figure 2d. It is worth noting that during the scan process, the top gate applies a fixed voltage only to modulate the energy band of the channel, while the bottom gate serves as the actual scanning voltage. This distinguishes it from the previously reported NCFETs including ferroelectrics.<sup>[44,45]</sup> In our configuration, the device can fully utilize the modulating ability of the ferroelectric gate, while avoiding the introduction of noticeable hysteresis in the transfer curve. The observations reveal that, despite the steepness of the transfer curve, the corresponding SS exceeds the benchmark of 60 mV dec<sup>-1</sup> upon setting  $V_{\text{CIPS}}$  to zero. In contrast, when nonzero voltages are applied to CIPS, there is a marked sharpening of the transfer curves. Simultaneously, a breakthrough of SS beyond the conventional limit of 60 mV dec<sup>-1</sup> can be achieved with current variations in the range of two to three orders of magnitude, at three distinct voltages (2.5, 3, and 3.2 V). These SS data points below 60 mV dec<sup>-1</sup>, are marked in the light red area represented in Figure 2d. The heterojunction TEFT demonstrates optimal performance at a  $V_{\text{CIPS}}$  of 3 V, with the minimum SS reaching a value of 28 mV dec<sup>-1</sup>. These experimental results provide strong evidence for the pronounced modulation capacity of CIPS on the channel.

www.advancedsciencenews.com

CIENCE NEWS

**Figure 2.** Schematic diagram and performance of heterojunction TFET. a) Schematic cross-section of WSe<sub>2</sub>/MoS<sub>2</sub> heterojunction device. b) The upper panel shows the side view for the crystal structure of CIPS with vdW gap between the layers with the polarization direction indicated by the arrow. The lower panel shows the band alignment conditions for band-to-band tunneling. c) Transfer curves with  $V_{CIPS}$  changing from 0 V to 3.2 V at  $V_{ds} = -1$  V. d)  $I_{ds}$  versus SS data extracted from the transfer curves shown in c).

The underlying mechanism was then subsequently illustrated in Figure 2b. CIPS, with an ABC-type stacked sulfur structure intercalated by elements such as copper (Cu) and indium (In) along with paired phosphorus (P-P), is used to regulate channel materials. Due to the broken symmetry in the lattice, the CIPS shows spontaneous electric polarization and ferroelectricity at temperatures below the Curie point. We maintained control over the experimental environment to ensure that the temperature remained below the Curie point of CIPS (315 K), thus safeguarding the unaltered ferroelectric properties of CIPS.<sup>[46]</sup> Characterization techniques performed at room temperature, such as PFM and Raman spectroscopy, provide additional evidence supporting the ferroelectric properties of the CIPS material utilized in our study. Applying an appropriate positive voltage on the top gate results in an upward shift of the WSe<sub>2</sub> band below CIPS. When the valence band of WSe<sub>2</sub> is positioned higher than the conduction band of MoS<sub>2</sub>, a staggered alignment is formed between the energy bands of the two materials. Figure S4 (Supporting Information) shows the band diagram of the heterojunction at different  $V_{CIPS}$  values. Under such band alignment, the empty density of states (DOS) in the valence band of WSe<sub>2</sub> aligns with the occupied DOS in the conduction band of  $MoS_2$ . When a  $V_{ds}$  is applied, electrons will undergo band-to-band tunneling from the valence band of WSe<sub>2</sub> to the conduction band of MoS<sub>2</sub>, resulting in the TFET being in the "on" state. It is worth noting that in the case of lightly p-doped WSe<sub>2</sub> with the Fermi level very close to or slightly below the valence band, there is a significant reduction in the number of electrons capable of tunneling into the n

region. As a result, a smooth transition from tunneling current to thermionic emission current occurs, exhibiting only a subtle NDR trend and no breakthrough on SS. The CIPS-induced bandto-band tunneling is further substantiated through temperaturedependent measurements. As illustrated in Figure S5a,b (Supporting Information), when the temperature is varied from 290 K to 90 K, the minimum and average SS values extracted from the transfer curve exhibit a near-constant stability. Therefore, the experimental results again validate the strong modulating ability of CIPS on 2D heterojunctions.

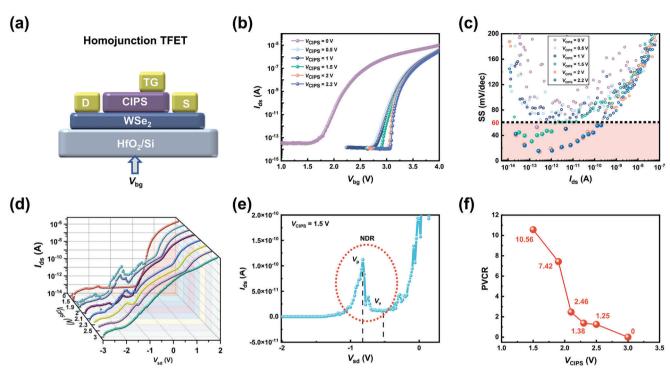

Although the heterojunction TFET displays a lower SS that surpasses the thermal emission limit, the construction of the heterojunction inevitably introduces defects that hamper device performance. To resolve this issue, we have considered replacing the heterojunction with a homojunction. By utilizing a bipolar WSe<sub>2</sub> as the channel material which can be arbitrarily modulated into either p-type or n-type characteristic. Homojunction devices based on WSe2 typically exhibit high carrier mobility, reconfigurable tunability, and ultrafast characteristics, making them suitable for low-power devices.<sup>[47,48]</sup> With the implementation of CIPS for creating a staggered band alignment, we successfully produced a homojunction TFET, as depicted in Figure 3a, along with the corresponding output characteristics presented in Figure S6a (Supporting Information). When the gate voltage is applied to polarize the CIPS into either an upward or downward polarized state, the WSe<sub>2</sub> channel beneath the controlling gate can be selectively configured into a desired doping state, thereby facilitating the formation of a homojunction. The

www.advelectronicmat.de

www.advancedsciencenews.com

SCIENCE NEWS

**Figure 3.** Schematic diagram and performance of homojunction TFET. a) Schematic cross-section of WSe<sub>2</sub> homojunction device. b) Transfer curves with  $V_{CIPS}$  changing from 0 V to 2.2 V at  $V_{ds} = 1 \text{ V. c}$ )  $I_{ds}$  versus SS data extracted from the transfer curves shown in b). d) Output curves with  $V_{CIPS}$  changing from 0 V to 3 V. e) Output curve at  $V_{CIPS} = 1.5 \text{ V}$  with significant NDR. f)  $V_{CIPS}$ -dependent PVCR extracted from the output curves shown in d).

corresponding band structure is shown in Figure S7 (Supporting Information), CIPS induces n-type or p-type doping on WSe<sub>2</sub> when V<sub>CIPS</sub> exceeds 0 V or falls below 0 V, respectively. The mechanism of controlling n- and p-type doping in WSe2 using ferroelectric CIPS is as described below. Downward polarization in the ferroelectric domain, induced by applying a sufficiently large positive polarizing voltage, leads to the accumulation of electrons in WSe<sub>2</sub>, thereby achieving n-type doping as illustrated in Figure S7a (Supporting Information). Reversely, since WSe<sub>2</sub> is a bipolar material, p-type doping can be achieved by applying a negative polarizing voltage to the CIPS, which induces upward polarization, as depicted in Figure S7b (Supporting Information). The transfer characteristics of the obtained homojunction TFET were measured under various fixed top gate voltages. As shown in Figure 3b, a significant shift in the transfer curve is observed by applying a non-zero top gate voltage when compared to the case with zero top gate voltage, while maintaining an on/off ratio exceeding 10<sup>8</sup>. As  $V_{\text{CIPS}}$  increases from 0 to 2.2 V, the transfer curve demonstrates a more pronounced steepness, a trend further substantiated by the corresponding SS (Figure 3c). Specifically, when the voltage applied to the top gate exceeds 1.5 V, the device can maintain an ultra-low SS of less than 60 mV dec<sup>-1</sup> over a wide current range of more than three orders of magnitude. The optimal performance is achieved at  $V_{\text{CIPS}} = 2$  V, where the minimum SS reaches 14.2 mV dec<sup>-1</sup> and the average SS is approximately 30.3 mV dec<sup>-1</sup>. Figure S5c,d (Supporting Information) presents the temperature-dependent measurements of the WSe<sub>2</sub> homojunction, the stable SS under various temperatures verify the band-to-band tunneling effect. The ultralow SS values demonstrate the effectiveness of CIPS on the construction of  $\mathrm{WSe}_2$  homojunction.

Upon further examination of the device's output curves at various  $V_{\text{CIPS}}$  (Figure 3d), a distinct NDR phenomenon is observed, which is the direct evidence of carrier transport dominated by band-to-band tunneling. When  $V_{ds}$  is less than  $V_p$  (the voltage at which the current reaches the peak), the filling state of the nregion conduction band and the empty state of the p-region valence band overlap, causing an increase in  $I_{ds}$ . As  $V_{ds}$  continues to increase, the overlapping states between the two regions decrease, leading to a reduction in current toward the valley point as Vv (the voltage at which the current reaches the valley).<sup>[19,49]</sup> Subsequently, the current exhibits a subsequent rise again as a result of the contribution of thermionic current. This phenomenon is particularly noticeable at  $V_{\text{CIPS}} = 1.5 \text{ V}$  (Figure 3e). Furthermore, an analysis of the peak-to-valley current ratio (PVCR) displayed by each curve in Figure 3d was conducted, and the PVCR- $V_{\text{CIPS}}$  plot is depicted in Figure 3f. The PVCR reaches a maximum of 10.56 when  $V_{\text{CIPS}}$  is adjusted to 1.5 V, highlighting the capacity of CIPS to effectuate a substantial doping of WSe<sub>2</sub>. It is of paramount importance to underscore that, in contrast to the heterojunction TFET, the SS values of the homojunction TFET show a remarkable downward trend and a correspondingly pronounced NDR phenomenon. This can be principally ascribed to enhanced tunneling resulting from the superior interface cleanliness inherent to the homojunction TFET. We also investigated the modulation capability of CIPS on the MoS<sub>2</sub> channel (Figure S8, Supporting Information). Regrettably, while CIPS exhibited a certain level of influence on MoS<sub>2</sub>, the impact was not as signifSCIENCE NEWS \_\_\_\_\_

www.advelectronicmat.de

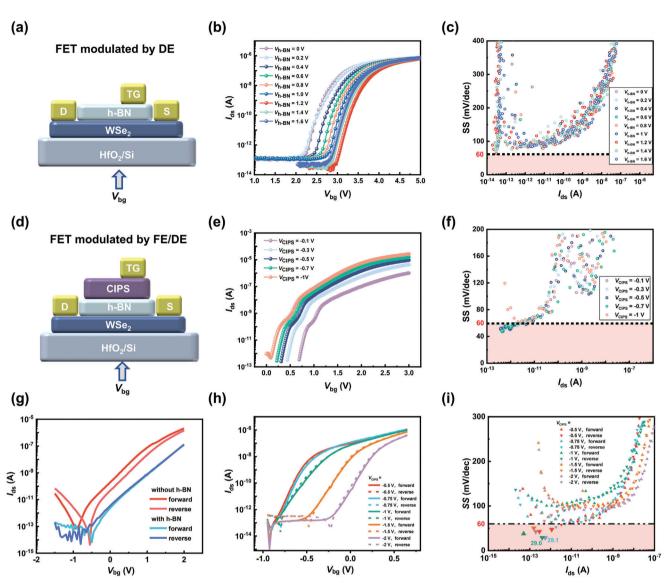

**Figure 4.** Schematic diagram and performance of FETs involved traditional dielectric gates. a) Schematic cross-section of WSe<sub>2</sub> FET modulated by h-BN. b) Transfer characteristics for various  $V_{CIPS}$  of the FET shown in (a), and c) the corresponding  $I_{ds}$  versus SS data extracted from the transfer curves. d) Schematic cross-section of WSe<sub>2</sub> FET modulated by both h-BN and CIPS. e) The transfer characteristics for various  $V_{h-BN}$  of the FET and f) corresponding  $I_{ds}$  versus SS data extracted from the transfer curves. g) The transfer curves with and without a dielectric layer show that the introduce of h-BN significantly reduce hysteresis of 7.69 mV. h) Transfer curve of CIPS/h-BN/WSe<sub>2</sub> devices with negligibly small hysteresis under different  $V_{CIPS}$ . i) The SS value extracted from (h) with a minimum of 29.0 mV dec<sup>-1</sup>.

icant as that for the WSe<sub>2</sub> homojunction. Furthermore, regardless of the different  $V_{\rm CIPS}$  values, the SS consistently did not exceed the limit of 60 mV dec<sup>-1</sup> limit. This observation aligns with our discussion that WSe<sub>2</sub>, given its bipolar nature, can achieve band-to-band tunneling, whereas  $\rm MoS_2$  does not exhibit the same behavior.

Importantly, unlike previous devices showing NDR, our device exhibits a remarkably outstanding PVCR through the modulation of CIPS.<sup>[50,51]</sup> In practical applications, this suggests an improvement in the ability to distinguish thresholds within multilevel logic circuits and enhanced modulation of signal features within analog circuits. Such characteristics are essential for integrating NDR devices into operational circuits, demonstrating the enormous potential of our device for practical circuit applications.

To further validate the efficacy of our adopted framework, we also examined the scenario involving traditional dielectric gates. **Figure 4a** and Figure **S9a** (Supporting Information) present the schematic representation and optical image of WSe<sub>2</sub> FET, respectively, exclusively regulated by h-BN. By employing conventional dielectric gates to apply voltage through h-BN for localized control of WSe<sub>2</sub>, the device not only manifests a reduced ON-state current, but also consistently achieves SS exceeding 60 mV dec<sup>-1</sup> (Figure 4b,c). This confirms that the conduction mechanism of the device remains as the conventional thermionic emission and is unable to surpass the Boltzmann limit. Importantly, while the

SS did not surpass the theoretical limit, its minimum value is noticeably in close proximity to 60 mV dec<sup>-1</sup>. This implies the high quality of our device fabrication and indirectly substantiates the reliability of our prior experimental results. In the device with ferroelectric/dielectric joint control (Figure 4d and Figure S9b, Supporting Information), both h-BN and CIPS are involved in the local regulation of the channel. Observations from the transfer curve (Figure 4e) and corresponding SS (Figure 4f) suggest that the control effect is notably weaker compared to the device solely controlled by CIPS, essentially failing to breach the limitation of 60 mV dec<sup>-1</sup>. The presence of the h-BN dielectric layer diminishes the enhancement effect of ferroelectric gate on SS performance, as it has the potential to act as a charge isolation layer, significantly impacting the regulation effect of CIPS on the channel. The observed discrepancy in performance further confirms that the tunneling, rather than negative capacitance, is the predominant mechanism in our device.

Additionally, h-BN effectively modulates the dielectric match of the device, leading to a substantial reduction in the hysteresis of the transfer curve. By appropriately tuning the thickness of h-BN, it is possible to realize a near-hysteresis-free device, although this may come at the expense of an increase in SS (Figure 4g,h and Figure S10, Supporting Information). We have achieved a minimum SS of 29.0 mV dec<sup>-1</sup> and a hysteresis window of about 7.69 mV (Figure 4h,i). In comparison to devices utilizing other channel materials, the integration of h-BN substantially mitigates hysteresis. At  $V_{\text{CIPS}} = 2$  V, the hysteresis is observed to be negligible exclusively in the device incorporating h-BN (Figure 4h and Figures S3d, S6b, and S8d, Supporting Information). These results suggest that with further design and optimization, the device shows potential for superior performance across multiple metrics. In comparison with other low-power FETs based on ferroelectric materials recently reported, as shown in Figure S11 (Supporting Information), our homojunction TFET simultaneously demonstrates a relatively low SS, excellent on/off ratio, and an almost negligible minor hysteresis.<sup>[52-59]</sup> These findings suggest significant potential for further development and optimization in the field of semiconductor devices.

#### 3. Conclusion

In summary, we have presented a comprehensive study on 2D TFET based on the van der Waals integration of ferroelectric CIPS with WSe<sub>2</sub> as well as MoS<sub>2</sub>. Attributable to the effective modulation induced by the CIPS ferroelectric gate, both heterojunction WSe<sub>2</sub>/MoS<sub>2</sub> and homojunction WSe<sub>2</sub> are able to achieve staggered band alignment, consequently facilitating the construction of low-power TFETs operating via band-to-band tunneling mechanism. The resulting WSe<sub>2</sub> homojunction TFET exhibits a minimum SS of 14.2 mV dec<sup>-1</sup> and a large on/off ratio of 10<sup>8</sup>, highlighting its potential for high-performance electronic applications. Our 2D devices effectively address the issue of defect intrusion inherent in bulk materials. By employing innovative 2D ferroelectric materials, it exhibits optimal low-power characteristics, whilst maintaining maximal simplicity in structure and manufacturing process. The device further showcases a tunable PVCR with a maximum value exceeding 10, testifying to its significant potential as an NDR device. Our findings provide strong evidence that 2D TFETs with ferroelectric gate hold significant potential as a paradigm for designing high-density and low-power devices, thereby unfolding a new trajectory towards the realization of advanced low-power apparatus.

# 4. Experimental Section

Device Fabrication: The MoS<sub>2</sub>/WSe<sub>2</sub>/h-BN/CIPS flakes were mechanically exfoliated from bulk crystals using the tape and the polydimethyl-siloxane (PDMS) film. For the homojunction devices, the WSe<sub>2</sub> flakes were transferred on the HfO<sub>2</sub>/Si substrate. To construct the heterojunction, the bottom layer material (MoS<sub>2</sub> or WSe<sub>2</sub>) was first transferred onto the substrate. Then, utilizing the high-precision transfer platform and dry transfer method, the top layer materials were successively transferred layer by layer with the PDMS acting as a transfer supporting layer. Subsequently, electron-beam lithography technique was used to pattern the electrodes including source, drain, and gate. The Cr/Au (5/50 nm) electrodes were deposited via a thermal evaporation process at the evaporation rate of 0.2 Å s<sup>-1</sup>. Finally, under the condition of 60 °C, the lift-off process took place in a hot acetone solution for a duration of 30 min.

Characterization of 2D Materials and Heterostructures: The heterostructure was characterized by scanning electron microscope. The Raman analysis of WSe<sub>2</sub>, MoS<sub>2</sub>, CIPS, and their heterostructures was measured using a Raman spectrometer (Horiba iHR550) with a laser wavelength of 633 nm and spot size of  $\approx 1 \,\mu$ m. The PFM measurement was carried out in a commercial atomic force microscope (MFP-3D, Asylum Research, Goleta, CA) using the dual alternative voltage resonance tracking (DART) model with the drive voltage of 2 V. To confirm the vertical stacking of the heterojunction, focused ion beam (FIB) sectioning of the heterojunction was first performed, followed by energy dispersive spectroscopy (EDS) and high-resolution transmission electron microscopy (TEM) for detailed analysis.

*Electrical Measurement:* All electrical measurements were performed using Keithley 4200A-SCS semiconductor parameter analyzer with a probe station under vacuum at room temperature.

# **Supporting Information**

Supporting Information is available from the Wiley Online Library or from the author.

## Acknowledgements

X.C., T.J., and H.W. contributed equally to this work. The authors gratefully acknowledge the support from the National Natural Science Foundation of China (52102124, 52102156, U20A20244, 5222206, 52021001), the National Key Research and Development Program of China (2021YFA0718800), and the Natural Science Foundation of Sichuan Province (2023NSFSC0993).

# **Conflict of Interest**

The authors declare no conflict of interest.

## **Data Availability Statement**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

## Keywords

2D homojunction, band-to-band tunneling, negative differential resistance, tunnel field-effect transistor, van der Waals ferroelectrics

**ADVANCED**

www.advelectronicmat.de

Received: June 11, 2024 Revised: September 30, 2024 Published online:

- [1] Q. Cao, J. Tersoff, D. B. Farmer, Y. Zhu, S. J. Han, Science 2017, 356, 1369

- [2] L. Yang, X. D. Huang, Y. Li, H. J. Zhou, Y. J. Yu, H. Bao, J. C. Li, S. G. Ren, F. Wang, L. Ye, Y. H. He, J. Chen, G. Y. Pu, X. Li, X. S. Miao, InfoMat 2023, 5, e12416.

- [3] G. Iannaccone, F. Bonaccorso, L. Colombo, G. Fiori, Nat. Nanotechnol. 2018, 13, 183.

- [4] B. C Malvika, K. Mummaneni, J. Electron. Mater. 2022, 51, 923.

- [5] D. E. Nikonov, I. A. Young, Proc. IEEE 2013, 101, 2498.

- [6] P. L. Liu, S. C. Lu, J. Liu, B. Xia, G. Y. Yang, M. Ke, X. Z. Zhao, J. R. Yang, Y. X. Liu, C. Y. Ge, G. J. Liang, W. Chen, X. Z. Lan, J. B. Zhang, L. Gao, J. Tang, InfoMat 2024, 6, e12497.

- [7] E. Pop, Nano Res. 2010, 3, 147.

- [8] W. G. Vandenberghe, A. S. Verhulst, B. Soree, W. Magnus, G. Groeseneken, O. Smets, M. Heyns, M. V. Fischetti, Appl. Phys. Lett. 2013, 102, 013510.

- [9] Y. Y. Illarionov, A. G. Banshchikov, D. K. Polyushkin, S. Wachter, T. Knobloch, M. Thesberg, L. Mennel, M. Paur, M. Stöger-Pollach, A. Steiger-Thirsfeld, M. I. Vexler, M. Walt, N. S. Sokolov, T. Mueller, T. Grasser, Nat. Electron. 2019, 2, 230.

- [10] H. Lu, A. Seabaugh, IEEE J. Electron Devices Soc 2014, 2, 44.

- [11] S. Salahuddin, S. Dattat, Nano Lett. 2008, 8, 405.

- [12] J. Lyu, J. Pei, Y. Z. Guo, J. Gong, H. L. Li, Adv. Mater. 2020, 32, 1906000.

- [13] K. Gopalakrishnan, P. B. Griffin, J. D. Plummer, IEEE Trans. Electron Devices 2005, 52, 69.

- [14] N. T. Duong, C. Park, D. H. Nguyen, P. H. Nguyen, T. U. Tran, D. Y. Park, J. Lee, D. A. Nguyen, J. H. Oh, Y. S. Yu, M. S. Jeong, Nano Today 2021, 40, 101263.

- [15] G. Fiori, F. Bonaccorso, G. Iannaccone, T. Palacios, D. Neumaier, A. Seabaugh, S. K. Banerjee, L. Colombo, Nat. Nanotechnol. 2014, 9, 1063.

- [16] X. Yan, C. S. Liu, C. Li, W. Z. Bao, S. J. Ding, D. W. Zhang, P. Zhou, Small 2017, 13, 1701478.

- [17] J. S. Miao, C. Leblanc, J. J. Wang, Y. Gu, X. W. Liu, B. K. Song, H. R. Zhang, S. Krylyuk, W. D. Hu, A. V. Davydov, T. Back, N. Glavin, D. Jariwala, Nat. Electron. 2022, 5, 744.

- [18] W. W. Fei, J. Trommer, M. C. Lemme, T. Mikolajick, A. Heinzig, Info-Mat 2022, 4, e12355.

- [19] T. Roy, M. Tosun, X. Cao, H. Fang, D. H. Lien, P. D. Zhao, Y. Z. Chen, Y. L. Chueh, J. Guo, A. Javey, ACS Nano 2015, 9, 2071.

- [20] Y. S. Ang, L. M. Cao, L. K. Ang, InfoMat 2021, 3, 502.

- [21] L. Britnell, R. V. Gorbachev, R. Jalil, B. D. Belle, F. Schedin, A. Mishchenko, T. Georgiou, M. I. Katsnelson, L. Eaves, S. V. Morozov, N. M. R. Peres, J. Leist, A. K. Geim, K. S. Novoselov, L. A. Ponomarenko, Science 2012, 335, 947.

- [22] A. Nourbakhsh, A. Zubair, M. S. Dresselhaus, T. Palacios, Nano Lett. 2016. 16. 1359.

- [23] Y. Liu, Y. Huang, X. F. Duan, Nature 2019, 567, 323.

- [24] W. L. Ma, B. Shabbir, Q. D. Ou, Y. M. Dong, H. Y. Chen, P. N. Li, X. L. Zhang, Y. R. Lu, Q. L. Bao, InfoMat 2020, 2, 777.

- [25] Z. H. Hu, X. Liu, P. L. Hernández-Martínez, S. S. Zhang, P. Gu, W. Du, W. G. Xu, H. V. Demir, H. Y. Liu, Q. H. Xiong, InfoMat 2022, 4, e12290.

- [26] C. W. Tan, S. P. Xu, Z. J. Tan, L. Z. Sun, J. X. Wu, T. R. Li, H. L. Peng, InfoMat 2019, 1, 390.

- [27] Y. Wang, J. C. Kim, R. J. Wu, J. Martinez, X. J. Song, J. Yang, F. Zhao, K. A. Mkhoyan, H. Y. Jeong, M. Chhowalla, Nature 2019, 568, 70.

- [28] G. R. Chen, A. L. Sharpe, P. Gallagher, I. T. Rosen, E. J. Fox, L. L. Jiang, B. S. Lyu, H. Y. Li, K. Watanabe, T. Taniguchi, J. Jung, Z. W. Shi, D. Goldhaber-Gordon, Y. B. Zhang, F. Wang, Nature 2019, 572, 215.

- [29] S. Kanungo, G. Ahmad, P. Sahatiya, A. Mukhopadhyay, S. Chattopadhyay, npj 2D Mater. Appl. 2022, 6, 83.

- [30] D. Sarkar, X. J. Xie, W. Liu, W. Cao, J. H. Kang, Y. J. Gong, S. Kraemer, P. M. Ajayan, K. Banerjee, Nature 2015, 526, 91.

- [31] S. Kim, G. Myeong, W. Shin, H. Lim, B. Kim, T. Jin, S. Chang, K. Watanabe, T. Taniguchi, S. Cho, Nat. Nanotechnol. 2020, 15, 203.

- [32] X. Xiong, M. Q. Huang, B. Hu, X. F. Li, F. Liu, S. C. Li, M. C. Tian, T. Y. Li, J. Song, Y. Q. Wu, Nat. Electron. 2020, 3, 106.

- [33] Y. Balaji, Q. Smets, A. Szabo, M. Mascaro, D. Lin, I. Asselberghs, I. Radu, M. Luisier, G. Groeseneken, Adv. Funct. Mater. 2020, 30, 1905970.

- [34] F. C. Liu, L. You, K. L. Seyler, X. B. Li, P. Yu, J. H. Lin, X. W. Wang, J. D. Zhou, H. Wang, H. Y. He, S. T. Pantelides, W. Zhou, P. Sharma, X. D. Xu, P. M. Ajayan, J. L. Wang, Z. Liu, Nat. Commun. 2016, 7, 12357;

- [35] S. Park, S. Oh, D. Lee, J. H. Park, InfoMat 2022, 4, e12367;

- [36] J. Niu, S. Jeon, D. Kim, S. Baek, H. H. Yoo, J. Li, J. S. Park, Y. Lee, S. Lee, InfoMat 2024, 6, e12490.

- [37] Y. Zhou, D. Wu, Y. H. Zhu, Y. J. Cho, Q. He, X. Yang, K. Herrera, Z. D. Chu, Y. Han, M. C. Downer, H. L. Peng, K. J. Lai, Nano Lett. 2017, 17, 5508

- [38] M. W. Si, P. Y. Liao, G. Qiu, Y. Q. Duan, P. D. D. Ye, ACS Nano 2018, 12.6700.

- [39] X. W. Wang, C. Zhu, Y. Deng, R. H. Duan, J. Q. Chen, Q. S. Zeng, J. D. Zhou, Q. D. Fu, L. You, S. Liu, J. H. Edgar, P. Yu, Z. Liu, Nat. Commun. 2021, 12, 1109

- [40] M. Y. Hong, X. K. Zhang, Y. Geng, Y. A. Wang, X. F. Wei, L. Gao, H. H. Yu, Z. H. Cao, Z. Zhang, Y. Zhang, InfoMat 2024, 6, 12491.

- [41] B. S. Liu, X. K. Zhang, J. L. Du, J. K. Xiao, H. H. Yu, M. Y. Hong, L. Gao, Y. Ou, Z. Kang, Q. L. Liao, Z. Zhang, Y. Zhang, InfoMat 2022, 4, e12282

- [42] X. Z. Sun, Y. Chen, Z. W. Li, Y. Han, Q. Zhou, B. B. Wang, T. Taniguchi, K. Watanabe, A. D. Zhao, J. L. Wang, Y. Liu, J. M. Xue, ACS Nano 2021, 15 e16314

- [43] P. H. Blessy, A. Shenbagavalli, T. S. A. Samuel, Silicon 2023, 15, 2385.

- [44] Z. Y. Liu, Y. L. Sun, Y. T. Ding, M. J. Li, X. Liu, Z. F. Liu, Z. M. Chen, J. Phys. Chem. Lett. 2023, 14, 6784.

- [45] I. Luk'yanchuk, A. Razumnaya, A. Sené, Y. Tikhonov, V. M. Vinokur, npj Comput. Mater. 2022, 8, 52.

- [46] T. Jia, Y. Chen, Y. Cai, W. Dai, C. Zhang, L. Yu, W. Yue, H. Kimura, Y. Yao, S. Yu, Q. Guo, Z. Cheng, Nanomaterials 2022, 12, 2516.

- [47] L. Mennel, J. Symonowicz, S. Wachter, D. K. Polyushkin, A. J. Molina-Mendoza, T. Mueller, Nature 2020, 579, 62.

- [48] C. Pan, C. Y. Wang, S. J. Liang, Y. Wang, T. J. Cao, P. F. Wang, C. Wang, S. Wang, B. Cheng, A. Y. Gao, E. F. Liu, K. Watanabe, T. Taniguchi, F. Miao, Nat. Electron. 2020, 3, 383.

- [49] Q. S. Lv, F. G. Yan, N. Mori, W. K. Zhu, C. Hu, Z. R. Kudrynskyi, Z. D. Kovalyuk, A. Patanè, K. Y. Wang, Adv. Funct. Mater. 2020, 30, 1910713.

- [50] J. H. Kim, S. Sarkar, Y. Wang, T. Taniguchi, K. Watanabe, M. Chhowalla, Nano Lett. 2024, 24, 2561.

- [51] N. Abraham, K. Murali, K. Watanabe, T. Taniguchi, K. Majumdar, ACS Nano 2020, 14, 15678.

- [52] A. Saeidi, T. Rosca, E. Memisevic, I. Stolichnov, M. Cavalieri, L. E. Wernersson, A. M. Ionescu, Nano Lett. 2020, 20, 3255;

- [53] Y. Wang, X. Y. Bai, J. W. Chu, H. B. Wang, G. F. Rao, X. Q. Pan, X. C. Du, K. Hu, X. P. Wang, C. H. Gong, C. J. Yin, C. Yang, C. Y. Yan, C. Y. Wu, Y. Shuai, X. F. Wang, M. Liao, J. Xiong, Adv. Mater. 2020, 32, 2005353.

- [54] K. Yang, S. L. Wang, T. Han, H. X. Liu, Nanomaterials 2021, 11, 1971

- [55] H. Cho, H. J. Jin, S. Lee, S. Jeon, Y. Cho, S. Park, M. Jang, L. J. Widiapradja, D. Ryu, J. H. Park, K. Kim, S. Im, Adv. Mater. 2023, 35, 2300478.

Adv. Electron. Mater. 2024, 2400463

RIGHTSLINK4)

ADVANCED SCIENCE NEWS \_\_\_\_

www.advancedsciencenews.com

#### www.advelectronicmat.de

- [56] H. Quan, D. H. Meng, X. Z. Ma, C. G. Qiu, ACS Appl. Mater. Interfaces 2023, 15, 45076.

- [57] L. Zhao, Y. S. Liang, J. Y. Ma, Z. D. Pan, X. T. Liu, M. M. Yang, Y. M. Sun, W. Gao, B. Li, J. B. Li, N. J. Huo, *Adv. Funct. Mater.* **2023**, *33*, 2306708.

- [58] S. Kamaei, X. Liu, A. Saeidi, Y. F. Wei, C. Gastaldi, J. Brugger, A. M. Ionescu, *Nat. Electron.* **2023**, *6*, 658.

- [59] J. Y. Zou, X. Zou, L. Liu, H. J. Wang, J. P. Xu, *IEEE Trans. Electron Devices* 2024, 71, 1185.

© 2024 The Author(s). Advanced Electronic Materials published by Wiley-VCH GmbH